31 KiB

31 KiB

file:: Computer_Organization_and_Design_1681729306797_0.pdf file-path:: ../../../../assets/Computer_Organization_and_Design_1681729306797_0.pdf

-

Computer Abstractions and Technology

ls-type:: annotation hl-page:: 25 hl-color:: yellow id:: 643d2848-6edf-4c05-92c7-4a7de1b9cd22 - Classes of Computing Applications and Their Characteristics ls-type:: annotation hl-page:: 28 hl-color:: yellow id:: 643e2b9c-0bc2-4b02-b2b1-33e25539d5b9

- Below Your Program

ls-type:: annotation

hl-page:: 36

hl-color:: yellow

id:: 643ea1cf-af0e-45ba-97b3-376fd21ee1e3

collapsed:: true

- From a High-Level Language to the Language of Hardware ls-type:: annotation hl-page:: 37 hl-color:: yellow id:: 643ea1d7-cd7d-4e81-8d6f-c268aab04f68

- Under the Covers

ls-type:: annotation

hl-page:: 39

hl-color:: yellow

id:: 643ea295-e170-403a-a43d-71777bb41d9b

collapsed:: true

- The five classic components of a computer are input, output, memory, datapath, and control ls-type:: annotation hl-page:: 40 hl-color:: yellow id:: 643ea2f7-1fa7-4c12-ad2d-34a90d6968b7

- liquid crystal displays (LCDs)

hl-page:: 41

ls-type:: annotation

id:: 643ea91c-7643-4563-9341-f85096313a3b

hl-color:: yellow

- The LCD is not the source of light but instead controls the transmission of light. There is a background light source and the LCD has many rods which bend light to make it pass through. When applied with a current, the rod no more bends light thus controlling the pixel.

- an active matrix that has a tiny transistor switch at each pixel to precisely control current and make sharper images ls-type:: annotation hl-page:: 41 hl-color:: yellow id:: 643ead73-e1a6-4f10-82c5-2760a4ce839f

- instruction set architecture

hl-page:: 45

ls-type:: annotation

id:: 643eb029-9fe9-4013-a4a2-1365e195333b

hl-color:: yellow

- interface between the hardware and low-level software, distinguish architecture from implementation

- Technologies for Building Processors and Memory

ls-type:: annotation

hl-page:: 47

hl-color:: yellow

id:: 643eb311-6b10-4fa3-9aa3-dfd5a59acf2c

collapsed:: true

- Semiconductor, silicon: add materials to silicon that allow tiny areas to transform into one of three devices: Excellent conductor, Excellent insulator and Transistor (conduct/insulate at some conditions) hl-page:: 48 ls-type:: annotation id:: 643eb66d-0294-46ab-a182-20021b2495c5 hl-color:: yellow

- Silicon ingot sliced into Blank wafers, processed into Patterned wafers, and then Tested wafer, diced into Tested dies, bonded to package, finally Tested packaged dies

- die: Rectangular sections cut from a wafer (actually chip)

- yield: Percentage of good dies from the total dies on the wafer

- Performance

ls-type:: annotation

hl-page:: 51

hl-color:: yellow

id:: 643ec3be-027e-48b5-90e0-cd4a5e901691

collapsed:: true

- response/execution time: time between the start and completion of a task

hl-page:: 52

ls-type:: annotation

id:: 643fb234-d566-4913-a03b-c574e6a623c4

hl-color:: yellow

\text{Performance}_X = \frac{1}{\text{Execution time}_X}- Relative Performance: A is ==n times as fast as== B, which means the same program runs for 1/n time on A of that on B hl-page:: 54 ls-type:: annotation id:: 643fe045-80bb-4c47-b601-3fdc9175581d hl-color:: yellow

- throughput: the total amount of work done in a given time hl-page:: 53 ls-type:: annotation id:: 643fb242-9401-42fa-bddc-d93e571b6e99 hl-color:: yellow

- Measuring Performance

ls-type:: annotation

hl-page:: 55

hl-color:: yellow

id:: 6440d1fd-a2c1-4d4c-a493-3b5c7d91448e

- Elapsed time: total time to complete a task, including RAM access, IO and other overhead.

- CPU time: time that CPU spends on computing for this task and not includes IO or waiting for schedule

- user CPU time

- system CPU time: time that OS performing tasks on behalf of the program (syscall?)

- CPU Performance and Its Factors

ls-type:: annotation

hl-page:: 56

hl-color:: yellow

id:: 6440d4c6-9dc2-4712-9d25-6386325581e5

- clock cycles: discrete time intervals

- clock period: length of a clock cycle

- clock rate: inverse of the clock period

- For a specific program, CPU time = CPU clock cycles

\timesClock cycle time = CPU clock cycles\divClock rate

- clock cycles: discrete time intervals

- Instruction Performance

ls-type:: annotation

hl-page:: 58

hl-color:: yellow

id:: 6440d70f-cde0-41ca-af1b-82d5a777a7a8

- CPU clock cycles = Instruction count

\timesCPI - CPI (clock Cycles Per Instruction): average number of cycles each instruction takes to execute (for one program)

- compare two different implementations of the same ISA

- CPU clock cycles = Instruction count

- The Classic CPU Performance Equation

ls-type:: annotation

hl-page:: 59

hl-color:: yellow

id:: 6440d99c-e080-4352-8c2d-7d35e897a2ee

- CPU time = Instruction count

\timesCPI\divClock rate - The formulas separates 3 key factors affecting the performance

- The only complete and reliable measure of computer performance is time. hl-page:: 61 ls-type:: annotation id:: 6440dc59-a80f-4185-9692-8e4122cad4b4 hl-color:: yellow

- CPI depends on a wide variety of design details in the computer hl-page:: 61 ls-type:: annotation id:: 6440dcd2-ae75-4a59-a2c5-aff6e3bf7953 hl-color:: yellow

- CPU time = Instruction count

- response/execution time: time between the start and completion of a task

hl-page:: 52

ls-type:: annotation

id:: 643fb234-d566-4913-a03b-c574e6a623c4

hl-color:: yellow

- The Power Wall

ls-type:: annotation

hl-page:: 63

hl-color:: yellow

id:: 6440df39-4ac7-4efc-b59a-64db6354ca0f

collapsed:: true

- dynamic energy: The energy consumed when transistors switch states, primary source of energy consumption for CMOS.

- The energy of a single transition:

\text{Energy} \propto \frac12 \times \text{Capacitive load} \times \text{Voltage}^2 - The power required per transistor:

\text{Power} \propto \frac12 \times \text{Capacitive load} \times \text{Voltage}^2 \times \text{Frequency switched}- Frequency switched is a function of the clock rate

- Capacitive load is a function of fanout (number of transistors connected to an output) and the technology (capacitance of wires and transistors).

- Main way to reduce power is to lower the voltage.

- There is problem with low voltage: this makes the capacitor leakage increase. (static energy)

- The Sea Change: The Switch from Uniprocessors to Multiprocessors

ls-type:: annotation

hl-page:: 66

hl-color:: yellow

id:: 6440e9ca-16a4-48ed-9648-adafb74ce097

- This section is about the difficulty of parallel programming and relative materials.

- Fallacies and Pitfalls

ls-type:: annotation

hl-page:: 72

hl-color:: yellow

id:: 6440ea56-fdd5-426f-9a76-d5b5a7465c55

collapsed:: true

- Amdahl's Law: $\text{Execution time after improvement} = \frac{\text{Execution time affected by improvement} }{\text{Amount of improvement}} + \text{Execution time unaffected}$

hl-page:: 72

ls-type:: annotation

id:: 6441179d-ae59-49b4-8903-874cb5b7c9cd

hl-color:: yellow

- Thus, we CANNOT expect ==improvement of one aspect== of a computer to ==increase overall performance by an amount proportional== to the size of improvement.

- Computers at low utilization don't necessarily use little power, or in other words, power consumption is not proportional to the system's load. hl-page:: 73 ls-type:: annotation id:: 6441212c-596a-463c-a47a-04478b16268b hl-color:: yellow

- MIPS (million instructions per second) = $\frac{\text{Instruction count}}{\text{Execution time} \times 10^6} = \frac{\text{Clock rate}}{\text{CPI} \times 10^6}$

hl-page:: 74

ls-type:: annotation

id:: 64412369-dd7a-4a26-9979-be7179f38df6

hl-color:: yellow

- Problem 1: it doesn't take into account the Instruction count, or the capability of each instruction. We should not compare computers with different ISAs.

- Problem 2: MIPS varies between programs even on the same computer.

- Problem 3: MIPS can vary independently from performance.

- Amdahl's Law: $\text{Execution time after improvement} = \frac{\text{Execution time affected by improvement} }{\text{Amount of improvement}} + \text{Execution time unaffected}$

hl-page:: 72

ls-type:: annotation

id:: 6441179d-ae59-49b4-8903-874cb5b7c9cd

hl-color:: yellow

- Word List 1

collapsed:: true

- omnipresent 无所不在的 ubiquitous hl-page:: 27 ls-type:: annotation id:: 643e2b82-f5a5-411e-9571-d494858c175a hl-color:: green

- credo 信条,教义 ls-type:: annotation hl-page:: 30 hl-color:: green id:: 643e473a-2f03-419b-ad3a-8309c33dff15

- unraveling 解开;阐明; hl-page:: 31 ls-type:: annotation id:: 643e47b3-cc6c-4fd1-83a9-0510b16a5e9c hl-color:: green

- acronyms 首字母缩略词 ls-type:: annotation hl-page:: 32 hl-color:: green id:: 643e485f-8de8-41bf-86ac-812ba202f4c8

- leverage 影响力;杠杆作用 hl-page:: 33 ls-type:: annotation id:: 643e4871-3ebb-4578-9227-b40a534adeac hl-color:: green

- intrinsic 固有的, 内在的, 本质的 ls-type:: annotation hl-page:: 33 hl-color:: green id:: 643e4882-a5ea-4bff-9b5f-17f585313142

- weave 编织;杜撰 hl-page:: 34 ls-type:: annotation id:: 643e492d-5e63-4b9b-93f7-4f44bf50158e hl-color:: green

- rod 杆;竿;棒 ls-type:: annotation hl-page:: 41 hl-color:: green id:: 643ea931-ff7e-4bd7-96d1-b7eab4dcc563

- helix n. 螺旋 hl-page:: 41 ls-type:: annotation id:: 643ea93a-fa50-486a-b74a-d96f2a4df9aa hl-color:: green

- raster 光栅 ls-type:: annotation hl-page:: 41 hl-color:: green id:: 643ea8f8-7e5f-42e3-a04a-01cd91f25d13

- brawn 体力;发达的肌肉 ls-type:: annotation hl-page:: 42 hl-color:: green id:: 643eaede-f413-4717-9136-e28363909bb3

- quadruple 四倍的;四重的; hl-page:: 48 ls-type:: annotation id:: 643eb37e-2927-4100-b8b3-c76bbe5450f4 hl-color:: green

- slam 砰地关上(门或窗);抨击 hl-page:: 65 ls-type:: annotation id:: 6440e306-7625-4883-b3f0-fbdca42d92e3 hl-color:: green

- faucet 水龙头 ls-type:: annotation hl-page:: 65 hl-color:: green id:: 6440e5e4-e02f-43e3-9311-64f8b6d67f75

- unwieldy ls-type:: annotation hl-page:: 65 hl-color:: green id:: 6440e73c-8061-47b2-bc37-522db24f1707

- startling ls-type:: annotation hl-page:: 66 hl-color:: green id:: 6440e8c9-0024-4751-8233-43e8cea16699

- stiffer ls-type:: annotation hl-page:: 68 hl-color:: green id:: 6440e99d-0c7d-4acb-9ba7-9172e1d383d8

- ensnared ls-type:: annotation hl-page:: 72 hl-color:: green id:: 6440ec21-aef2-4494-8b50-d16a83c0d9bb

- corollary ls-type:: annotation hl-page:: 72 hl-color:: green id:: 6441170f-b51b-453a-b612-0b71b2b6032d

- demoralize ls-type:: annotation hl-page:: 72 hl-color:: green id:: 64411718-be78-469d-9b83-0dfd9c83338b

- plague ls-type:: annotation hl-page:: 72 hl-color:: green id:: 64411720-4c6a-49ce-8a72-4aa19e7b8482

- preclude ls-type:: annotation hl-page:: 75 hl-color:: green id:: 6440ebb6-a98d-465f-8345-3da49486f653

- constituent ls-type:: annotation hl-page:: 75 hl-color:: green id:: 6440ebc6-59b1-4b7e-ae67-75559989873b

- impeachable ls-type:: annotation hl-page:: 75 hl-color:: green id:: 6440ebd7-8c0c-4a18-9d86-bd95714f58ac

-

Instructions: Language of the Computer

ls-type:: annotation hl-page:: 83 hl-color:: yellow id:: 64412821-6b54-47a0-9317-a4b042989fdf - Operations of the Computer Hardware

ls-type:: annotation

hl-page:: 86

hl-color:: yellow

id:: 64412ca1-c9b5-4d6b-ba19-d353992dd2f1

collapsed:: true

- Three-operand arithmetic instructions

- Operands of the Computer Hardware

ls-type:: annotation

hl-page:: 89

hl-color:: yellow

id:: 64412cc0-59a8-4a38-9094-1a7bd916a41f

collapsed:: true

- Registers, where operands of arithmetic instructions must reside

- Register size is a word (32 bit)

- 32 registers in MIPS.

- fewer registers to keep clock cycles fast (though 31 regs may not be faster then 32 regs)

- instruction format (5-bit field for register number)

- data transfer instructions

ls-type:: annotation

hl-page:: 91

hl-color:: yellow

id:: 64412fc0-7ad1-4c8a-9c03-c198e741605b

- memory to register or inverse

- alignment restriction: words must start at addresses that are multiples of 4. As a result, there is some restrictions on the address for

lw/swhl-page:: 92 ls-type:: annotation id:: 6441425c-134d-449d-ae39-4db48a67054c hl-color:: yellow - memory is addressed by byte, remember this especially when dealing with array indices because the type of array elements decides the offset.

- MIPS is in the big-endian camp (though the textbook says so, the latest MIPS32 by default is little endian) hl-page:: 93 ls-type:: annotation id:: 64414940-7d06-4339-af0b-974b1b34dbc5 hl-color:: yellow

- Constant or Immediate Operands

ls-type:: annotation

hl-page:: 95

hl-color:: yellow

id:: 64414a51-2d38-48ff-b0c0-bc53f9c5fadb

- Constant operands occur frequently, and by ==including constants inside arithmetic instructions==, operations are much ==faster== and use ==less energy== than if constants were ==loaded from memory==. hl-page:: 95 ls-type:: annotation id:: 64414af2-05ea-4a88-baf6-a19462b4c3a9 hl-color:: yellow

- Since MIPS supports ==negative constants==, there is no need for subtract immediate in MIPS. ls-type:: annotation hl-page:: 96 hl-color:: yellow id:: 64414b4e-cf31-4e7f-8320-2f1bbcbf9b32

- Registers, where operands of arithmetic instructions must reside

- Signed and Unsigned Numbers

ls-type:: annotation

hl-page:: 96

hl-color:: yellow

id:: 64414b5f-de73-4bbc-812d-8ebd0f082ea0

collapsed:: true

- binary digits

hl-page:: 96

ls-type:: annotation

id:: 64414bb1-c764-493b-b555-4e241a31f255

hl-color:: yellow

- value of

ith digit:d \times \text{Base}^i - LSB and MSB

- Numbers have infinite number of digits, binary bit patterns are simply representatives of numbers. Thus, there are various ways of handling overflow. hl-page:: 97 ls-type:: annotation id:: 64414c34-4dc9-4127-9938-faf0374b6c29 hl-color:: yellow

- value of

- Signed numbers

- sign and magnitude: add a separate sign bit. Problems with this approach, need an extra step to set the sign during calculation, negative and positive zero hl-page:: 98 ls-type:: annotation id:: 64414d4d-71a4-44df-9475-d710bfee40d3 hl-color:: yellow

- two's compliment

- the value of this form can be written as

(d_{31} \cdot -2^{31}) + d_{30} \cdot 2^{30} + \dots, note the first-2^{31}

- the value of this form can be written as

- one's compliment: negate operation is to simply invert each bit

- sign extension: copy the sign repeatedly to fill the rest of the register when loading from memory

hl-page:: 99

ls-type:: annotation

id:: 64414fbb-4773-4332-bf21-f533847d0bde

hl-color:: yellow

- This trick works because positive 2's complement numbers really have an infinite number of 0s on the left and negative 2's complement numbers have an infinite number of 1s. The binary bit pattern representing a number hides leading bits to fit the width of the hardware; sign extension simply restores some of them. hl-page:: 101 ls-type:: annotation id:: 64415085-a9e5-4193-a5d1-9c90f5d63ea8 hl-color:: yellow

- binary digits

hl-page:: 96

ls-type:: annotation

id:: 64414bb1-c764-493b-b555-4e241a31f255

hl-color:: yellow

- Representing Instructions in the Computer

ls-type:: annotation

hl-page:: 103

hl-color:: yellow

id:: 64414d2f-3ea8-45a6-9a7a-b84f74a554cf

collapsed:: true

- MIPS Fields

ls-type:: annotation

hl-page:: 105

hl-color:: yellow

id:: 64415179-3df0-431e-9e53-8608796931dd

- In order to keep the instructions regular (aligned by word), MIPS has irregular layouts for different types of instruct.

- R-type:

op | rs | rt | rd | shamt | funct - I-type:

op | rs | rt | constant/address- The 16-bit address means a

lwcan only load from a region of\pm 2^{15}bytes of the base register. - here

rtserves as the destination register

- The 16-bit address means a

- MIPS Fields

ls-type:: annotation

hl-page:: 105

hl-color:: yellow

id:: 64415179-3df0-431e-9e53-8608796931dd

- Logical Operations

ls-type:: annotation

hl-page:: 110

hl-color:: yellow

id:: 64415118-595d-4125-b641-333d82a58006

collapsed:: true

sllandsrl, use theshamt(shift amount) fieldandioriextend their 16-bit constant field by filling 0s- there is no exact instruction for bitwise not, but a

nor(not or,a NOR b = NOT(a OR b)) instruction (perhaps in order to keep the 3-operand format)

- Instructions for Making Decisions

ls-type:: annotation

hl-page:: 113

hl-color:: yellow

id:: 644154b4-a07e-46fd-aa88-178297b61434

collapsed:: true

- conditional branches:

bneandbeqhl-page:: 113 ls-type:: annotation id:: 644156a7-b2b5-4010-97e3-a432f077cd33 hl-color:: yellow - Loops ls-type:: annotation hl-page:: 115 hl-color:: yellow id:: 64415778-92af-4d30-b3b4-0b3dddd397f4

sltandslti: ifrs < rt/rs < immthenrd=1elserd=0- MIPS assemblers use the combination

slt/sltiandbeq/bneand$zeroto create all relative conditions sltu/stliusigned and unsigned comparison are different, thus an unsigned version is provided

- MIPS assemblers use the combination

- Case/Switch Statement: jump address table and

jrinstruction (the runtime destination address is stored in register) hl-page:: 118 ls-type:: annotation id:: 644159a7-3b96-4924-8260-0cb300307c86 hl-color:: yellow

- conditional branches:

- Supporting Procedures in Computer Hardware

ls-type:: annotation

hl-page:: 119

hl-color:: yellow

id:: 644156f5-e485-4140-be11-6ef87a585383

collapsed:: true

jaljumps to an address and simultaneously saves the address of the following instruction in$rajrjumps to the address specified in a register- Calling convention for register:

$a0-$a3: four argument registers in which to pass parameters$v0–$v1: two value registers in which to return values$ra: one return address register to return to the point of origin$t0–$t9: temporary registers that are not preserved by the callee on a procedure call id:: 644163d9-8d4b-43e8-acec-57a835c4ce48$s0–$s7: saved registers that must be preserved on a procedure call (if used, callee saves and restores them)$sp: stack pointer to the most recently allocated address,pushsubstract from$spandpopadd to$sp$fp: frame pointer to the first word of the frame of a procedure$gp: pointer to global static data

- FIGURE 2.11 What is and what is not preserved across a procedure call. ls-type:: annotation hl-page:: 125 hl-color:: yellow id:: 64416615-2966-4adb-a524-845337e588d3

- Allocating Space for New Data on the Stack

ls-type:: annotation

hl-page:: 126

hl-color:: yellow

id:: 6441667f-2639-458b-91fd-8bf6b5a2c6ae

- stack is also used to store variables that are local to the procedure but do not fit in registers

- procedure frame or activation record ls-type:: annotation hl-page:: 126 hl-color:: yellow id:: 64416688-3f6e-444e-b265-3e4a36ec51b8

- a frame pointer offers a stable base register within a procedure for local memory-references, in that stack pointer changes during the procedure

- ASCII and String

hl-page:: 129

ls-type:: annotation

id:: 644167c0-1ac2-42df-b01d-4fff03a393e7

hl-color:: yellow

collapsed:: true

lb/lbuandsbload/store the right most byte,lh/lhuandshload/store the lower half word- Some notes about how to organize a string

- character size

- length or end mark

- MIPS Addressing for 32-bit Immediates and Addresses

ls-type:: annotation

hl-page:: 134

hl-color:: yellow

id:: 6441f1a7-4442-466f-9edc-776f6e0e6ecb

collapsed:: true

- 32-Bit Immediate Operands:

luiloads a half word to the upper 16 bits of a register, and then aorisets the lower 16 bits, thus loading a 32-bit immediate hl-page:: 135 ls-type:: annotation id:: 6441fb16-91e4-42d8-94bf-5718dd9fc91b hl-color:: yellow - Addressing in Branches and Jumps

ls-type:: annotation

hl-page:: 136

hl-color:: yellow

id:: 64427722-3a05-43f1-b00e-7dcc30cc74ff

- J-type instruction:

op | address (26 bits) - Since MIPS instructions are all 4-byte aligned, the unit of the address in PC-relative addressing is actually word. For example, 16-bit address in branch instruction actually represents an 18-bit address.

- J-type instruction:

- MIPS Addressing Mode

ls-type:: annotation

hl-page:: 139

hl-color:: yellow

id:: 64427a40-988f-4430-aaa5-84d3926c6234

-

- Immediate addressing: the operand is a constant within the instruction itself (e.g.,

addi $rd, $rs, 4) - Register addressing: the operand is a register (e.g.,

add $rd, $rs, $rt) - Base (displacement) addressing: the operand is at the memory location whose address is the sum of a register and a constant in the instruction (e.g.,

lw $rd, 4($rs)) - PC-relative addressing: the branch address is the sum of the PC and a constant in the instruction (e.g.,

beq $rs, $rt, #addr) - Pseudo-direct addressing: the jump address is the 26 bits of the instruction concatenated with the upper bits of the PC (e.g.,

j #addr)

- Immediate addressing: the operand is a constant within the instruction itself (e.g.,

-

- 32-Bit Immediate Operands:

- Parallelism and Instructions: Synchronization

ls-type:: annotation

hl-page:: 144

hl-color:: yellow

id:: 644284b0-dd95-46e5-829f-4509200e5f8d

collapsed:: true

- a set of hardware primitives with the ability to atomically read and modify a memory location hl-page:: 144 ls-type:: annotation id:: 64428547-07fb-49e2-9e3f-a7ac95b7e8e0 hl-color:: yellow

- atomic exchange: interchange a value in a register for a value in memory

- Introduces some challenges in the processor design

while (xchg(&lock, 1) == 1) ;

- MIPS

ll/sc: a pair of instructions in which the second instruction returns a value showing whether the pair of instructions as if one atomic instruction.while (ll(&lock) == 1 && sc(&lock, 1)) ;scwill fail after either another attempted store to thelled address or ==any exception==. It is possible to create deadlock wheresccan never complete due to repeated page faults.

- Translating and Starting a Program

ls-type:: annotation

hl-page:: 146

hl-color:: yellow

id:: 64428b6e-1dba-4bd4-ab91-d18ae9cb9cf6

collapsed:: true

- Assembler

ls-type:: annotation

hl-page:: 147

hl-color:: yellow

id:: 64428b72-2291-4380-a2ad-dc5cdc82315e

- pseudoinstructions: assembler translates these instructions into equivalent machine instructions. Register

$atis reserved for such translations. hl-page:: 147 ls-type:: annotation id:: 64428b7b-0678-4fc3-a105-71fdc6185144 hl-color:: yellow- Example 1:

move $t0, $t1->add $t0, $t1, $zero - Example 2:

blt $t0, $t1, LABEL1->slt $at, $t0, $t1; bne $at, $zero, LABEL1

- Example 1:

- The assembler turns the assembly language program into an object file, which is a combination of ==machine language instructions==, ==data==, and information needed to place instructions properly in memory (==symbol table==, ==relocation information==). hl-page:: 148 ls-type:: annotation id:: 64428ce2-cd44-4d6d-a311-dc7aa3f656ab hl-color:: yellow

- The object file for UNIX systems typically contains six distinct pieces: object file header, text segment, static data segment, relocation information, symbol table, and debug information hl-page:: 148 ls-type:: annotation id:: 64428f56-bd42-4cc4-a4dd-bf8b05e76fc3 hl-color:: yellow

- pseudoinstructions: assembler translates these instructions into equivalent machine instructions. Register

- Linker

ls-type:: annotation

hl-page:: 149

hl-color:: yellow

id:: 64428f9a-632e-4bdb-80d5-56febc2bb977

- Re-compile the whole program at each change to a single procedure is huge waste, so compile/assemble independently and finally link them together.

- 3 steps for the linker:

- hl-page:: 149

ls-type:: annotation

id:: 6442909f-b0b5-4706-8454-f89466e3ff7e

hl-color:: yellow

- Place code and data modules symbolically in memory.

- Determine the addresses of data and instruction ==labels==.

- Patch both the internal and external ==references==.

- hl-page:: 149

ls-type:: annotation

id:: 6442909f-b0b5-4706-8454-f89466e3ff7e

hl-color:: yellow

- Example Problem: Linking Object Files hl-page:: 150 ls-type:: annotation id:: 6442957a-fb16-4069-8e74-d470c01ba18c hl-color:: yellow

- Dynamically Linked Libraries

ls-type:: annotation

hl-page:: 152

hl-color:: yellow

id:: 644292fb-c10c-43f6-8152-941b009e14c2

- Library routines are not linked and loaded until the program is run. Keep extra info on the location and name of non-local procedures. hl-page:: 152 ls-type:: annotation id:: 644295c2-95e3-4da8-ba89-5470c9049fce hl-color:: yellow

- The program loader uses the extra information to find the proper libraries and ==update all external references==.

- Lazy procedure linkage: Instead of linking all library routines that might be called, link only those are actually called at runtime.

- Assume there is a table of entries for external routines, at static linkage stage, set them all to a dummy address of a dynamic linker/loader. At runtime, the program jumps to this dummy address, and executes this linker/loader which finds the desired routine, remaps it and changes the address in the indirect jump location. Next time this routine is called, this indirect jump will go to the desired routine.

- Assembler

ls-type:: annotation

hl-page:: 147

hl-color:: yellow

id:: 64428b72-2291-4380-a2ad-dc5cdc82315e

- A C Sort Example to Put It All Together

ls-type:: annotation

hl-page:: 155

hl-color:: yellow

id:: 6442a0c7-e518-46f3-979d-9c104093343b

- Skipped, since it is easy

- Arrays versus Pointers

ls-type:: annotation

hl-page:: 164

hl-color:: yellow

id:: 6442a0b8-5961-423d-bbcf-96cf55fd55cf

- An example piece of code which iterate over an array by both pointer and index

- Skipped, since it is easy

- Advanced Material: Compiling C and Interpreting Java

ls-type:: annotation

hl-page:: 168

hl-color:: yellow

id:: 6442a09e-3edb-4593-833a-626506177900

- Skipped, since it is compiler's job (Control Flow Graph???)

- Real Stuff: ARMv7 (32-bit) Instructions ls-type:: annotation hl-page:: 194 hl-color:: yellow id:: 6442a15d-dfe5-49b0-9b78-5f109e674e2f

- Real Stuff: x86 Instructions ls-type:: annotation hl-page:: 198 hl-color:: yellow id:: 6442a152-baff-4ccb-aee2-2f548e14903e

- Real Stuff: ARMv8 (64-bit) Instructions

ls-type:: annotation

hl-page:: 207

hl-color:: yellow

id:: 6442a1ad-0491-48d7-84b7-7feba159d9dd

- The philosophy of ARMv8 is much closer to MIPS than ARMv7. For example, the

$zero, thebeq/bneinstead of the condition bit

- The philosophy of ARMv8 is much closer to MIPS than ARMv7. For example, the

- Design Principles

collapsed:: true

- Design Principle 1: Simplicity favors regularity. ls-type:: annotation hl-page:: 88 hl-color:: yellow id:: 644152b5-ee31-4da9-86e4-33d7472f04c3

- Design Principle 2: Smaller is faster. ls-type:: annotation hl-page:: 90 hl-color:: yellow id:: 644152aa-00c2-4542-abaf-7048e6d37904

- Design Principle 3: Good design demands good compromises. ls-type:: annotation hl-page:: 106 hl-color:: yellow id:: 64415292-0727-4366-8717-ecca11267baf

- Word List 2

- palatable ls-type:: annotation hl-page:: 86 hl-color:: green id:: 64412a38-84ed-4f97-b83d-911772eb7158

- rationale ls-type:: annotation hl-page:: 86 hl-color:: green id:: 64412bbd-513c-4e00-8576-7ef88749e552

- moot ls-type:: annotation hl-page:: 99 hl-color:: green id:: 64414e6e-e6f7-4d05-865f-a18455c509ba

- dichotomy ls-type:: annotation hl-page:: 117 hl-color:: green id:: 6441591a-02ed-4556-8fd7-5fdb310063e7

- spill ls-type:: annotation hl-page:: 121 hl-color:: green id:: 64416330-597c-4245-8d53-a5dc643ea05f

- wax and wane ls-type:: annotation hl-page:: 127 hl-color:: green id:: 64416671-9318-4296-9588-c0421c02cdd2

- interpose ls-type:: annotation hl-page:: 144 hl-color:: green id:: 64428502-8d37-4bad-a24f-6edfa9796740

- succinct ls-type:: annotation hl-page:: 148 hl-color:: green id:: 64428c72-5e4f-4f33-a1ac-cadd4610f04a

- stitch ls-type:: annotation hl-page:: 149 hl-color:: green id:: 6442903b-ae86-4608-8d83-60771782b088

- anatomy ls-type:: annotation hl-page:: 168 hl-color:: green id:: 64429b75-4433-4e39-8085-ad2e791dbf33

- brethren ls-type:: annotation hl-page:: 207 hl-color:: green id:: 6442a2eb-dfe3-4d2b-a54f-d483376198ff

- headstart ls-type:: annotation hl-page:: 207 hl-color:: green id:: 6442a2ee-8c2e-4ed2-a67f-23db50972a71

- toil hl-page:: 209 ls-type:: annotation id:: 6442a05d-69ba-4161-9ffa-bb305a17fcf1 hl-color:: green

-

Arithmetic for Computers

hl-page:: 225 ls-type:: annotation id:: 6442a5d0-e073-4cd4-a6c6-1bb664ee952a hl-color:: yellow - Word List 3

- quirks ls-type:: annotation hl-page:: 227 hl-color:: green id:: 64433ef2-0591-499f-b056-b2664d81156e

- Addition and Subtraction

ls-type:: annotation

hl-page:: 227

hl-color:: yellow

id:: 64433f1c-c023-429e-88d0-46cad778477c

- Addition is to add digits bit by bit from right to left with carries passed to the left digit.

- Subtraction uses addition, negate the second operand before adding.

- Overflow

- The result cannot be represented with the hardware.

- ==No overflow== can occur when ==adding operands with different signs== or ==subtracting operands with the same sign==.

- Overflow occurs when adding 2 positives and the sum is negative, or vice versa; and when subtracting a negative from a positive and get a negative, or vice versa.

- For a software detection, you can use

xorto detect sign difference. - For overflow (carry) of unsigned numbers, though often ignored, use the inequation

(\text{MAXUINT})2^{32}-1 \lt A + B \rightarrow 2^{32}-1 -A \lt B \rightarrow \overline{A} \lt B

- For a software detection, you can use

- In MIPS,

add/addi/subcauses exceptions on overflow; whileaddu/addiu/subudoes not cause exceptions on overflow.- Since C ignores overflow, it always uses

*uinstructions.

- Since C ignores overflow, it always uses

- saturating operation: When overflow, set the result to the MAX/MIN value rather than a modulo to 2^32 hl-page:: 230 ls-type:: annotation id:: 644347f7-9833-4208-99f7-655f94b5a7b5 hl-color:: yellow

- Multiplication

ls-type:: annotation

hl-page:: 232

hl-color:: yellow

id:: 64434f2d-d63b-4840-96da-918f7a04cb97

- Names of the operands:

product = multiplicand * multiplier - Observation

- n-bit multiplicand and m-bit multiplier result in a (m+n)-bit product (overflow)

- The manual multiplication method in essence is a ==shift-and-add== process.

- Sequential Version of the Multiplication Algorithm and Hardware

ls-type:: annotation

hl-page:: 233

hl-color:: yellow

id:: 64435253-b5bf-4832-ad91-025cede3bafd

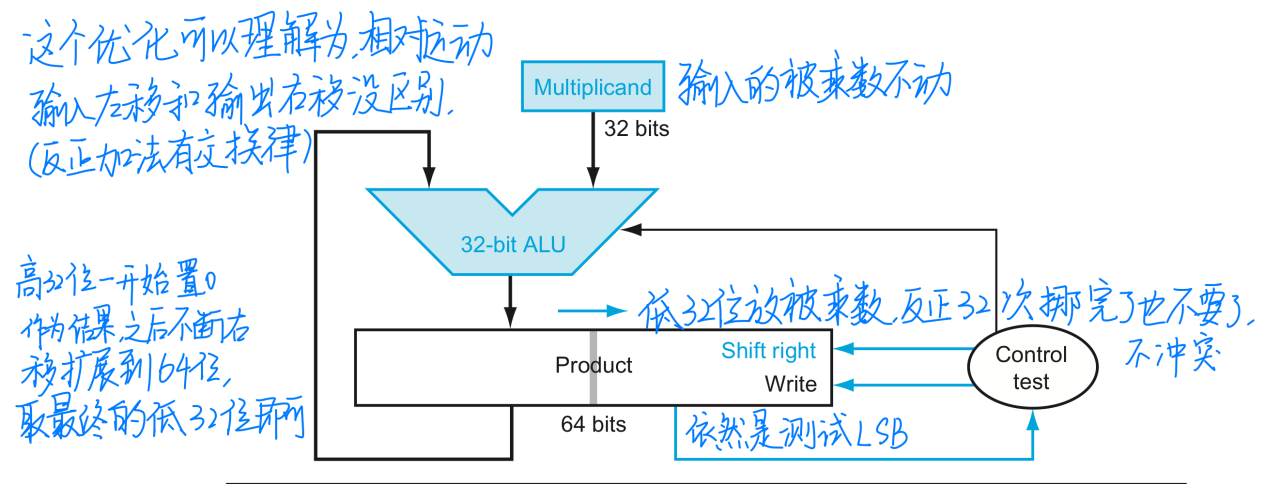

{:height 223, :width 449}

{:height 223, :width 449}- Pseudo code for the algorithm

uint64_t sequential_multiplier(uint32_t A, uint32_t B) { uint64_t multiplicand = A; uint32_t multiplier = B; uint64_t product = 0; for (int i = 0; i < 32; ++ i) { // 1. test the LSB of multiplier if (multiplier & 0x1) product += multiplicand; // else do nothing, or add 0 // 2 multiplicand <<= 1; // 3 multiplier >>= 1; } } - Though the textbook says that each iteration takes 3 clock cycles, I think all these can be done in 1 cycle (虽然时序会比较垃圾就是了). The following refined version no doubt needs only 1 cycle each iteration.

- Refined version: needs only one 64-bit register for product, and only one step operation to the register, shift right.

- Signed Multiplication

ls-type:: annotation

hl-page:: 236

hl-color:: yellow

id:: 64435d8f-d70f-4968-be40-ddbf8ef5a19e

- The easiest solution is that, first convert all operands to positive and calculate the sign separately; after multiplication, convert the the product to its correct sign.

- Names of the operands:

- vexing ls-type:: annotation hl-page:: 232 hl-color:: green id:: 64434f3c-f512-4f58-a6f2-05e7aa355ec6